Page 48 - 第三代半導體明日之星---碳化矽功率元件近況與展望

P. 48

DESIGN IDEAS

PPA(V):可變工作電壓最佳化效能功耗比

作者:James Chuang,新思科技資深產品行銷經理

效能功耗比(performance-per- watt)已成為確保設計品質的最 優先考量事項之一,這導致技術 重點與設計功耗最佳化方法轉 變。「變動式工作電壓」(variable operating voltage)在最佳化效能 功耗比成果方面具有極大潛力, 但這需有一種準確且有效的簽核 方法。

外,用於HPC設計的運算密集型工 作負載也導致幾乎不間斷的切換, 進而使功耗分佈大量地受到動態功 耗主導。這項分量顯示電晶體在各 狀態間切換時所消耗的功率。

米FinFET設計的個案研究顯示, 僅是降低5%的工作電壓,就能使 動態功耗降低9%。

高效能運算持續挑戰先進製 程節點PPA極限

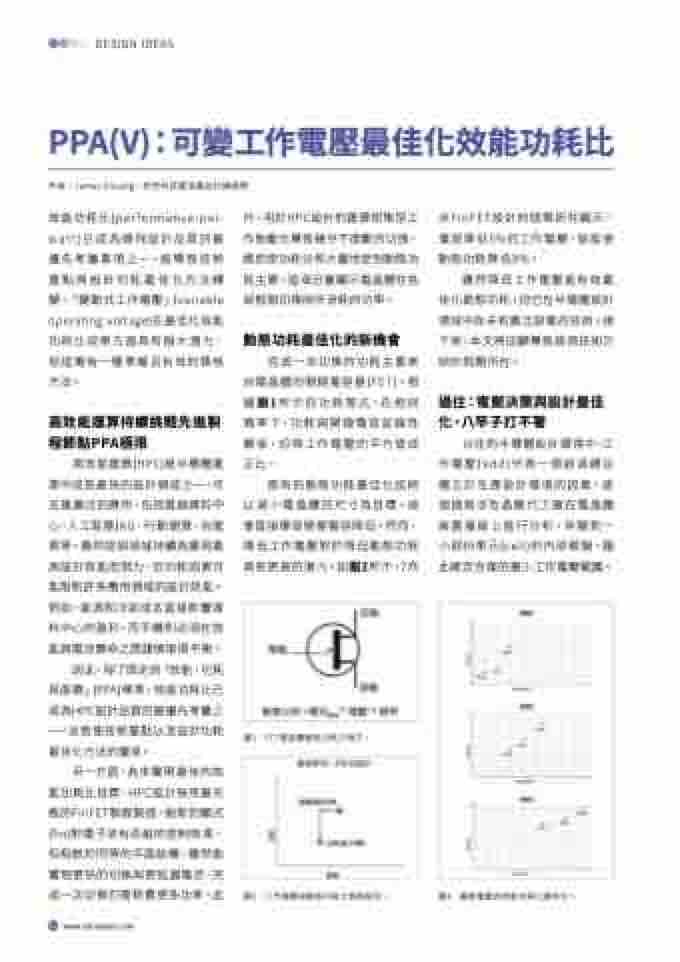

完成一次切換的功耗主要來 自電晶體的閘極電容器(FET)。根 據圖1所示的功耗等式,在相同 頻率下,功耗與閘極電容呈線性 關係,但與工作電壓的平方值成 正 比。

過往:電壓決策與設計最佳 化,八竿子打不著

高效能運算(HPC)是半導體產 業中成長最快的設計領域之一,可 支援廣泛的應用,包括雲端資料中 心、人工智慧(AI)、行動運算、自駕 車等。雖然這個領域持續為實現最 高設計效能而努力,但功耗因素可 能限制許多應用領域的設計效能。 例如,能源和冷卻成本直接影響資 料中心的盈利,而手機則必須在效 能與電池壽命之間謹慎取得平衡。

既有的動態功耗最佳化技術 以減小電晶體的尺寸為目標,這 會直接導致閘極電容降低。然而, 降低工作電壓對於降低動態功耗 具有更高的潛力。如圖2所示,7奈

以往的半導體設計環境中,工 作電壓(Vdd)代表一個經演繹且 獨立於生產設計環境的因素。這 個過程涉及晶圓代工廠在電晶體 裝置層級上進行分析,伴隨對一 小部份單元(cell)的內部模擬,藉 此確定合理的最小工作電壓範圍。

動態功耗最佳化的新機會

雖然降低工作電壓能有效最 佳化動態功耗,但它在半導體設計 領域中尚未有廣泛部署的技術。接 下來,本文將回顧導致這項技術欠 缺的問題所在。

因此,除了既定的「效能、功耗 與 面 積 」( P P A ) 標 準,效 能 功 耗 比 已 成為HPC設計品質的最優先考量之 一,並致使技術重點以及設計功耗 最佳化方法的變革。

圖1:FET電晶體動態功耗方程式。

圖2:工作電壓與動態功耗之個案研究。

另一方面,為求實現最佳的效 能功耗比目標,HPC設計採用最先 進的FinFET製程製造。創新的鰭式 (fin)對電子流有卓越的控制效果, 但相較於同等的平面結構,雖然能 實現更快的切換與更低漏電流,完 成一次切換仍需耗費更多功率。此

圖3:離散電壓的效能功耗比最佳化。

46 www.edntaiwan.com