Page 50 - 第三代半導體明日之星---碳化矽功率元件近況與展望

P. 50

DESIGN IDEAS

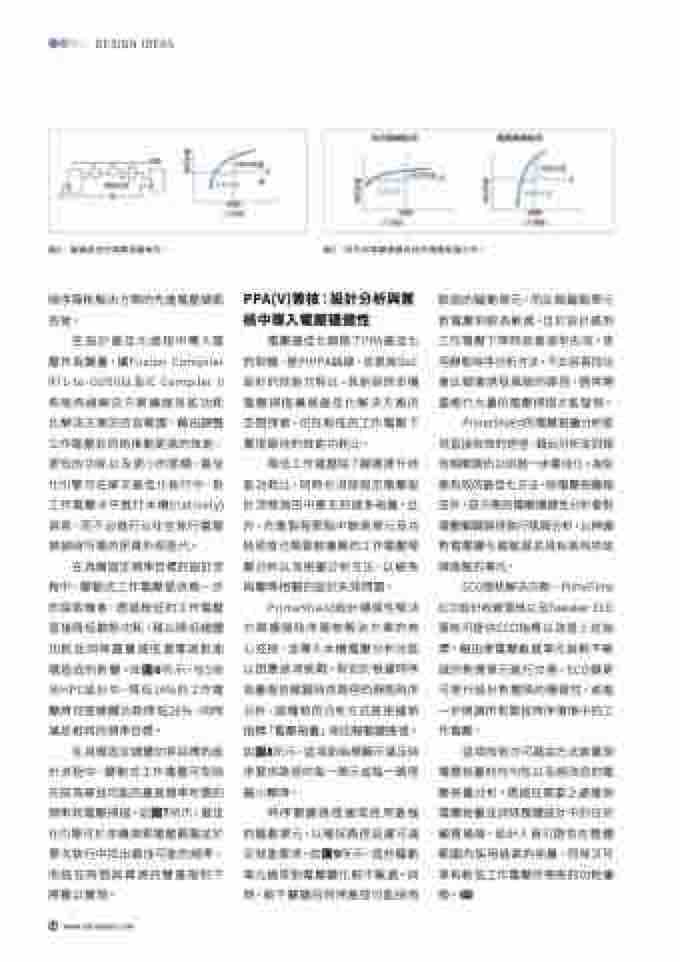

圖8:關鍵路徑的電壓裕量報告。

在設計最佳化過程中導入電 壓作為變量,讓Fusion Compiler RTL-to-GDSII以及IC Compiler II 佈局佈線解決方案擴展效能功耗 比解決方案的合宜範圍。藉由調整 工作電壓並同時推動更高的效能、 更低的功耗以及更小的面積,最佳 化引擎可在單次最佳化執行中,對 工作電壓水平進行本機(natively) 探索,而不必進行以往在執行電壓 掃描時所需的昂貴外部迭代。

圖9:時序與電壓關鍵路徑的電壓裕量分析。

時序簽核解決方案的先進電壓調節 技術。

PPA(V)簽核:設計分析與簽 核中導入電壓穩健性

較弱的驅動單元,而此類驅動單元 對電壓則較為敏感,且於設計遇到 工作電壓下降時就會提早失效。使 用靜態時序分析方法,不太容易找出 會此類會誘發風險的路徑,通常需 要進行大量的電壓掃描才能發現。

在具備固定頻率目標的設計流 程中,變動式工作電壓提供進一步 的探索機會,透過較低的工作電壓 直接降低動態功耗,藉以降低總體 功耗並同時盡量減低漏電與對面 積造成的影響。如圖6所示,在5奈 米HPC設計中,降低14%的工作電 壓將可使總體功耗降低26%,同時 滿足相同的頻率目標。

降低工作電壓除了顯著提升效 能功耗比,同時也消除固定電壓設 計流程無形中產生的過多裕量。此 外,先進製程節點中較高單元及功 耗密度也需要較複雜的工作電壓降 壓分析以及裕量分析方法,以避免 與壓降相關的設計失效問題。

ECO簽核解決方案─PrimeTime ECO設計收斂簽核以及Tweaker ECO 簽核可提供ECO指導以改善上述指 標。藉由將電壓敏感單元與較不敏 感的對應單元進行交換,ECO變更 可提升設計對壓降的穩健性,或進 一步微調所有簽核時序情境中的工 作電壓。

在具備固定總體功耗目標的設 計流程中,變動式工作電壓可免除 先前為尋找可能的最高頻率所需的 頻率和電壓掃描。如圖7所示,最佳 化引擎可於本機探索電壓範圍並於 單次執行中找出最佳可能的頻率, 而這在時間與資源的雙重限制下 將難以實現。

PrimeShield設計穩健性解決 方案擴展時序簽核解決方案的核 心技術,並導入本機電壓分析功能 以因應這項挑戰。有別於根據時序 裕量報告關鍵時序路徑的靜態時序 分析,這種新的分析方式是依據新 指標「電壓裕量」來回報關鍵路徑。 如圖8所示,這項新指標顯示滿足時 序要求路徑的每一單元或每一路徑 最小壓降。

這項技術亦可藉由方法論實現 電壓裕量的均勻性以及經改良的電 壓裕量分析。透過在需要之處確保 電壓裕量並消除整體設計中的任何 顯著風險,設計人員可避免在整體 範圍內採用過高的裕量,同時又可 享有較低工作電壓所帶來的功耗優 勢。

48 www.edntaiwan.com

電壓最佳化開啟了PPA最佳化 的契機,提升PPA曲線,並提高SoC 設計的效能功耗比。其創新的本機 電壓掃描擴展最佳化解決方案的 空間探索,可在較低的工作電壓下 實現最佳的效能功耗比。

PrimeShield的電壓裕量分析提 供直接有效的途徑,藉此分析並回報 告相關資訊以供進一步最佳化。為促 進有效的最佳化方法,除電壓裕量報 告外,該方案的電壓穩健性分析會對 電壓關鍵路徑執行瓶頸分析,以辨識 對電壓變化最敏感並具有高時序故 障風險的單元。

時序關鍵路徑通常使用最強 的驅動單元,以確保路徑延遲可滿 足效能要求。如圖9所示,這些驅動 單元通常對電壓變化較不敏感。同 時,較不關鍵的時序路徑可能採用