Page 22 - 第三代半導體明日之星---碳化矽功率元件近況與展望

P. 22

COVER STORY

蕭特基位障二極體(SBD)

金氧半場效應電晶體 (MOSFET)

100cm2/V-sec以上,是各大廠商以 及學術機構努力的方向。

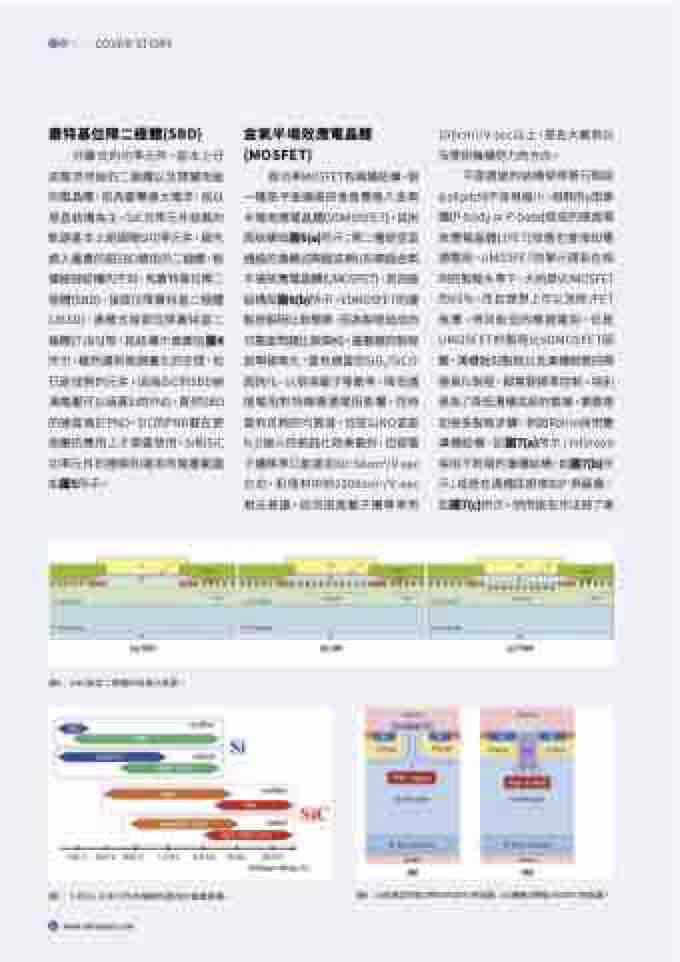

分離式的功率元件,基本上分 成整流用途的二極體以及開關用途 的電晶體,因為要導通大電流,故以 垂直結構為主。SiC功率元件發展的 軌跡基本上是跟隨Si功率元件,最先 進入量產的是SBD類型的二極體,根 據細部結構的不同,有蕭特基位障二 極體(SBD)、接面位障蕭特基二極體 (JBSD)、溝槽式接面位障蕭特基二 極體(TJBS)等,其結構示意圖如圖4 所示,雖然還有微調優化的空間,但 已是成熟的元件。因為SiC的SBD崩 潰電壓可以涵蓋Si的PND,既然SBD 的速度高於PND,SiC的PND要在更 高壓的應用上才需要使用,Si和SiC 功率元件的種類和適用的電壓範圍 如圖5所示。

高功率MOSFET有兩種結構,第 一種是平面通道的垂直雙植入金氧 半場效應電晶體(VDMOSFET),其剖 面結構如圖6(a)所示;第二種是垂直 通道的溝槽式閘極或稱U形閘極金氧 半場效應電晶體(UMOSFET),其剖面 結構如圖6(b)所示。VDMOSFET的優 點是製程比較簡單,因為製程造成的 可靠度問題比較單純。最關鍵的製程 是閘極氧化,要有適當的SiO2/SiC介 面鈍化,以提高載子移動率,降低通 道電阻對特徵導通電阻影響,同時 要有足夠的可靠度。目前以NO或是 N2O退火的氮鈍化效果最好,但是電 子遷移率只能達到30~50cm2/V-sec 左右,和塊材中的1000cm2/V-sec 相去甚遠,如何提高載子遷移率到

平面通道的結構使得單元間距 (cell pitch)不容易縮小,相鄰的p型基 體(P-body or P-base)造成的接面場 效應電晶體(JFET)效應也會增加導 通電阻。UMOSFET的單元間距在相 同的製程水準下,大約是VDMOSFET 的60%,而且理想上可以消除JFET 效應,得到較低的導通電阻。但是 UMOSFET的製程比VDMOSFET困 難,溝槽蝕刻製程以及溝槽側壁的閘 極氧化製程,都需要精準控制。特別 是為了降低溝槽底部的電場,需要增 加很多製程步驟,例如Rohm採用雙 溝槽結構,如圖7(a)所示;Infineon 採用不對稱的溝槽結構,如圖7(b)所 示;或是在溝槽底部增加P+屏蔽層, 如圖7(c)所示。然而這些作法除了增

圖4:SBD類型二極體的結構示意圖。

圖5:Si和SiC功率元件的種類和適用的電壓範圍。

圖6:(a)垂直型的高功率VDMOSFET剖面圖;(b)溝槽式閘極UMOSFET剖面圖。

20 www.edntaiwan.com