Page 23 - 第三代半導體明日之星---碳化矽功率元件近況與展望

P. 23

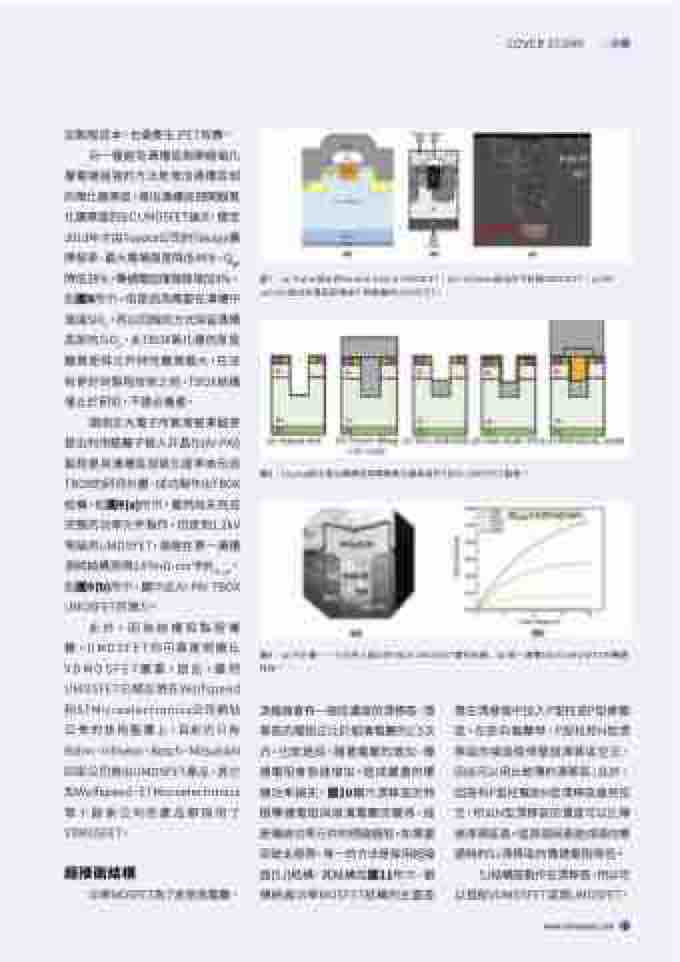

加製程成本,也會產生JFET效應。 另一種避免溝槽底部閘極氧化 層電場過強的方法是增加溝槽底部 的氧化層厚度,增加溝槽底部閘極氧 化層厚度的SiC UMOSFET論文,遲至 2013年才由Toyota公司的Takaya團 隊發表,最大電場強度降低46%,Qgd 降低38%,導通電阻僅微微增加4%, 如圖8所示。但是因為需要在溝槽中 填滿SiO2,再以回蝕刻方式保留溝槽 底部的SiO2,此TBOX氧化層的厚度 變異使得元件特性變異偏大,在沒 有更好的製程技術之前,TBOX結構

圖7:(a) Rohm提出的Double trench UMOSFET;(b) Infineon提出的不對稱UMOSFET;(c)Mit- subishi提出在溝底部增加P+屏蔽層的UMOSFET。

圖8:Toyota提出增加溝槽底部閘極氧化層厚度的TBOX UMOSFET製程。

圖9:(a)子計畫一、三主持人提出的TBOX UMOSFET實作結構;(b)單一溝槽TBOX UMOSFET的導通 特性。

汲極端會有一個低濃度的漂移區,漂 移區的電阻正比於崩潰電壓的2.5次 方,也就是說,隨著電壓的增加,導 通電阻會急速增加,造成嚴重的導 通功率損失。圖10顯示漂移區的特 徵導通電阻與崩潰電壓的關係,這 是傳統功率元件的理論極限。如果要 突破此極限,唯一的方法是採用超接 面(SJ)結構,其結構如圖11所示,跟 傳統高功率MOSFET結構的主要差

僅止於研究,不適合量產。 陽明交大電子所教授崔秉鉞曾

提出利用氬離子植入非晶化(Ar-PAI) 製程提高溝槽底部氧化速率來形成 TBOX的研究計畫,成功製作出TBOX 結構,如圖9(a)所示。雖然尚未完成 完整的功率元件製作,但是對1.2kV 等級的UMOSFET,曾經在單一溝槽 測試結構測得2.07mΩ-cm2的Ron,sp, 如圖9(b)所示,顯示此Ar-PAI TBOX UMOSFET的潛力。

此 外,因 為 結 構 和 製 程 複 雜,UMOSFET的可靠度問題比 VDMOSFET嚴重,因此,雖然 UMOSFET已經出現在Wolfspeed 和STMicroelectronics公司網站 公佈的技術藍圖上,目前仍只有 Rohm、Infineon、Bosch、Mitsubishi 四家公司推出UMOSFET產品,其它 如Wolfspeed、STMicroelectronics 等十餘家公司的產品都採用了 VDMOSFET。

異在漂移區中加入P型柱或P型摻雜 區。在逆向偏壓時,P型柱和N型漂 移區的接面使得整個漂移區空乏, 因此可以用比較薄的漂移區;此外, 因為有P型柱幫助N型漂移區達到空 乏,所以N型漂移區的濃度可以比傳 統漂移區高。這兩個因素造成順向導 通時的SJ漂移區的導通電阻降低。

超接面結構

SJ結構是製作在漂移區,所以可 以搭配VDMOSFET或是UMOSFET,

功率MOSFET為了承受高電壓,

COVER STORY

www.edntaiwan.com 21