Page 40 - 毫米波助攻 加速落實5G藍圖

P. 40

DESIGN FEATURES

imec的解決方案包含在用於 形成SOT層的硬光罩中嵌入鐵磁 體。有了此鐵磁體,在磁穿隧接面 的自由層能感應到一小部份均勻的 平面磁場。除了保留SOT-MRAM元 件的次奈秒寫入,這個方法也已經 證實十分可靠。此外,它還允許磁 穿隧接面的特性以及無磁場切換 的特性分別地進行最佳化。

雖然這些結果為最低快取層 的SRAM提供了替代路徑,SOT- MRAM仍然存在一個主要的缺 點:耗用面積。儘管具有類似柱狀 結構的STT-MRAM是一種雙端元 件,但SOT-MRAM則是三端的元 件——將兩個電晶體合併到一個 單元以及一個相對大的選擇器電 晶體(以滿足寫入裝置所需的較大 電流)。因此,迫切需要密度微縮方 面的創新,使其成為SRAM在低層 快取應用的真正競爭對手。

第二個改進是,imec將磁性 硬光罩嵌入於磁穿隧接面的頂端。 這消除了VCMA切換期間對外部磁 場的需求,提高了元件的可製造 性,而不至於降低其效能。

可製造性的另一個關注焦點 涉及熱預算:處理磁性層的熱預 算必須與整體製造流程相容。在 VLSI 2021,imec展示了一款後段

電壓控制的MRAM運作被探 索作為進一步降低STT-MRAM 功耗的方法之一。儘管寫入STT- MRAM記憶體單元透過電流執行,

38 www.edntaiwan.com

VCMA-MRAM:超低功率的 由此所產出的元件製造利用

冠軍

imec 300mm的最新技術基礎架 構,並經證實其與CMOS技術相 容。可靠的1.1GHz (或是奈秒級 速度)無外部磁場自由VCMA切換, 因而只使用20fJ的寫入能量,達到

但壓控磁各向異性(VCMA)- MRAM 則利用電磁場(在此是指電壓)執行 其寫入作業——大幅降低了能耗。 為了將自由層從平行(P)狀態切換 到反平行狀態(AP)(或反之亦然), 需要兩個基本元件:一個電場(穿 隧屏障)以消除能量屏障,以及一 個供實際VCMA切換的外部平面

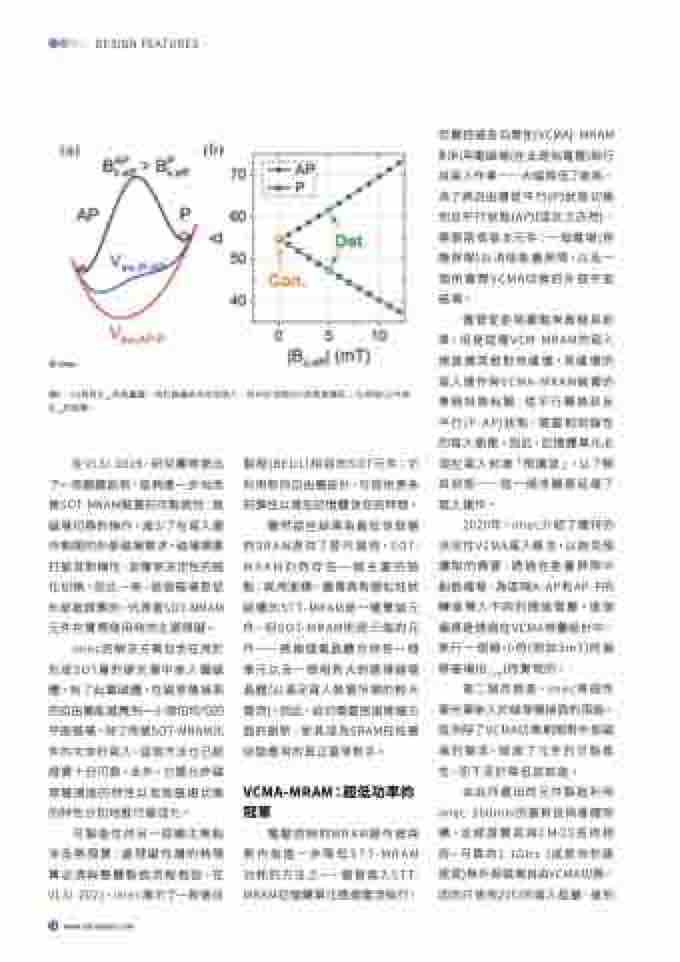

圖4:(a)具有Bz,eff的能量圖,用於提議的決定性寫入,其中AP狀態比P狀態更穩定;(b)保留(Δ)作為 Bz.eff的函數。

磁場。儘管從能耗觀點來看極具前 景,但是這種VCM-MRAM的寫入 速度通常相對地緩慢。其緩慢的 寫入運作與VCMA-MRAM裝置的 單極特質有關:從平行轉換到反 平行(P-AP)狀態,需要相同極性 的寫入脈衝。因此,記憶體單元必 須在寫入前被「預讀取」,以了解 其狀態——這一順序顯著延緩了 寫入運作。

在VLSI 2019,研究團隊提出 了一項關鍵創新,能夠進一步地改 善SOT-MRAM裝置的可製造性:無 磁場切換的操作,減少了在寫入運 作期間的外部磁場需求。磁場需要 打破其對稱性,並確保決定性的磁 化切換。如此一來,這個磁場是從 外部被誘導的,代表著SOT-MRAM 元件在實際使用時的主要障礙。

製程(BEOL)相容的SOT元件;它 利用新的自由層設計,可提供更多 的彈性以增加記憶體保存的時間。

2020年,imec介紹了獨特的 決定性VCMA寫入概念,以避免預 讀取的需要:透過在能量屏障中 創造偏移,為區隔A-AP和AP-P的 轉換導入不同的閥值電壓。這個 偏移是透過在VCMA堆疊設計中, 執行一個極小的(例如5mT)的偏 移磁場(Bz,eff)而實現的。