Page 38 - 毫米波助攻 加速落實5G藍圖

P. 38

DESIGN FEATURES

上,imec展示了在5nm技術節點 導入以STT-MRAM作為最後一層 (L3)快取記憶體的可行性。這個 分析是以設計-技術的協同最佳 化和矽驗證模式為基礎的,並揭 露了STT-MRAM能夠符合在高效 能運算領域中對於最後一層快取 記憶體的效能需求。此外,STT- MRAM單元僅佔SRAM巨集43.3% 的面積;以高密度記憶體單元來 看,STT-MRAM也比SRAM更具有 能源效益。

創新,imec等研究機構並著眼 於開發相容於CMOS相容的基於 300mm整合流程,讓這些MRAM 產品更易於製造。該團隊聚焦於具 有垂直磁化的MRAM類型裝置,因 為相較於平面磁化技術,它更具備 擴展的潛力。

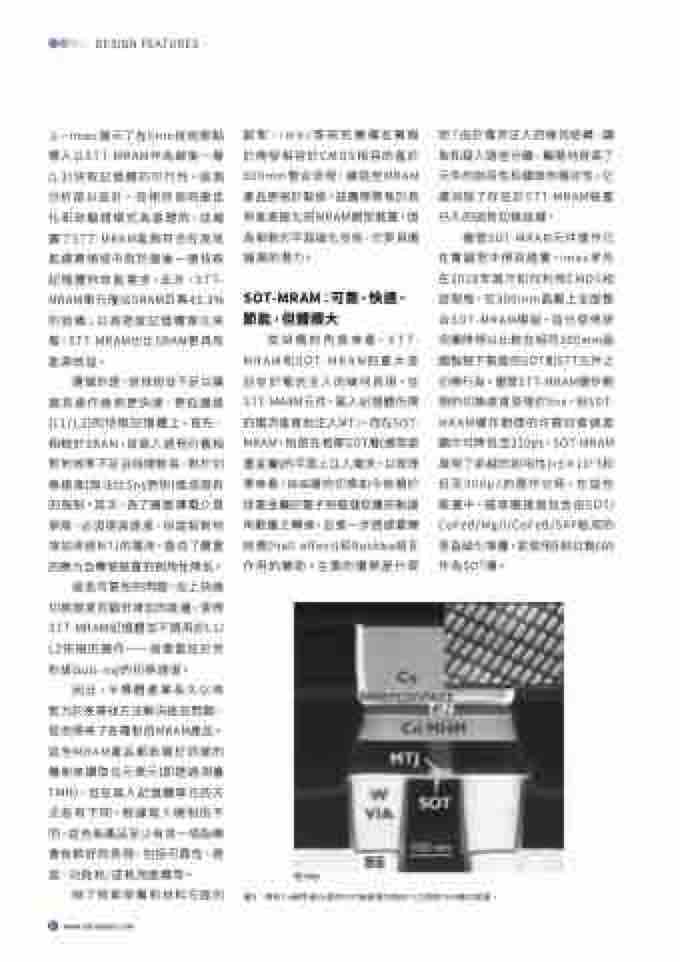

從架構的角度來看,STT- MRAM和SOT-MRAM的最大差 別在於電流注入的幾何表現。在 STT-MARM元件,寫入記憶體所需 的電流垂直地注入MTJ。而在SOT- MRAM,則是在相鄰SOT層(通常是 重金屬)的平面上注入電流。以物理 學來看,自由層的切換如今依賴於 從重金屬的電子到磁儲存層的軌道 角動量之轉換,並進一步透過霍爾 效應(Hall effect)和Rashba相互 作用的輔助。主要的優勢是什麼

呢?由於電流注入的幾何結構,讀 取和寫入路徑分離,顯著地提高了 元件的耐用性和讀取的穩定性。它 還消除了存在於STT-MRAM裝置 已久的固有切換延遲。

遺憾的是,該技術並不足以擴 展其操作達到更快速、更低層級 (L1/L2)的快取記憶體上。首先, 相較於SRAM,其寫入過程仍舊相 對地效率不足且時間較長,對於切 換速度(無法比5ns更快)造成既有 的限制。其次,為了通過薄電介質 屏障,必須提高速度,但這相對地 增加流經MTJ的電流,造成了嚴重 的應力且導致裝置的耐用性降低。

這些可靠性的問題,加上快速 切換速度而額外增加的能量,使得 STT-MRAM記憶體並不適用於L1/ L2快取的運作——這需要低於奈 秒級(sub-ns)的切換速度。

S O T - M R A M:可 靠、快 速、 節 能,但 體 積 大

儘管SOT-MRAM元件運作已 在實驗室中得到證實,imec率先 在2018年展示如何利用CMOS相 容製程,在300mm晶圓上全面整 合SOT-MRAM模組。這也使得研 究團隊得以比較在相同300mm晶 圓製程下製造的SOT和STT元件之 切換行為。儘管STT-MRAM運作期 間的切換速度受限於5ns,但SOT- MRAM運作期間的可靠切換速度 顯示可降低至210ps。SOT-MRAM 展現了卓越的耐用性(>5×1010)和 低至300pJ的運作功耗。在這些 裝置中,磁穿隧接面包含由SOT/ CoFeB/MgO/CoFeB/SAF組成的 垂直磁化堆疊,並使用β相位鎢(W) 作為SOT層。

因此,半導體產業長久以來 致力於來尋找方法解決這些問題, 從而帶來了各種新的MRAM產品。 這些MRAM產品都依賴於同樣的 機制來讀取位元單元(即透過測量 TMR),但在寫入記憶體單元的方 式各有不同。根據寫入機制的不 同,這些新產品至少有某一項指標 會有較好的表現,包括可靠性、速 度、功耗和/或耗用面積等。

除了探索架構和材料方面的

圖3:帶有Co磁性硬光罩的SOT無磁場切換MTJ之側面TEM橫切面圖。

36 www.edntaiwan.com