Page 38 - 材料分析層層把關先進製程設備零缺陷

P. 38

DESIGN IDEAS

設計實例

提高IC設計中數位邏輯速度的六 種技巧

作者:Deekshith Krishnegowda,Marvell Technology 晶片設計工程師

設計人員在開發晶片邏輯之前,必須在許多因素之間作出權衡。例如,如果是為行動應用開發晶片,功 耗就是一個非常重要的因素。在這種情況下,需要低功耗邏輯。顧名思義,低功耗邏輯有助於降低功 耗,但 會 影 響 晶 片 的 性 能。同 樣 地,如 果 是 為 資 料 中 心 應 用 開 發 晶 片,則 需 考 慮 高 性 能,功 耗 相 對 次 之。

總之,晶片的功耗和性能是 成反比的。在為晶片設計編寫邏 輯時,設計人員必須找到功耗和 性能的適當平衡。如前所述,晶片 的高速度對於某些應用來說是必 須的。因此,在為此類應用開發邏 輯時,有一些方法可以透過少量的 邏輯最佳化來提高設計速度。本 文介紹可用於提高晶片設計速度 的技巧和訣竅。

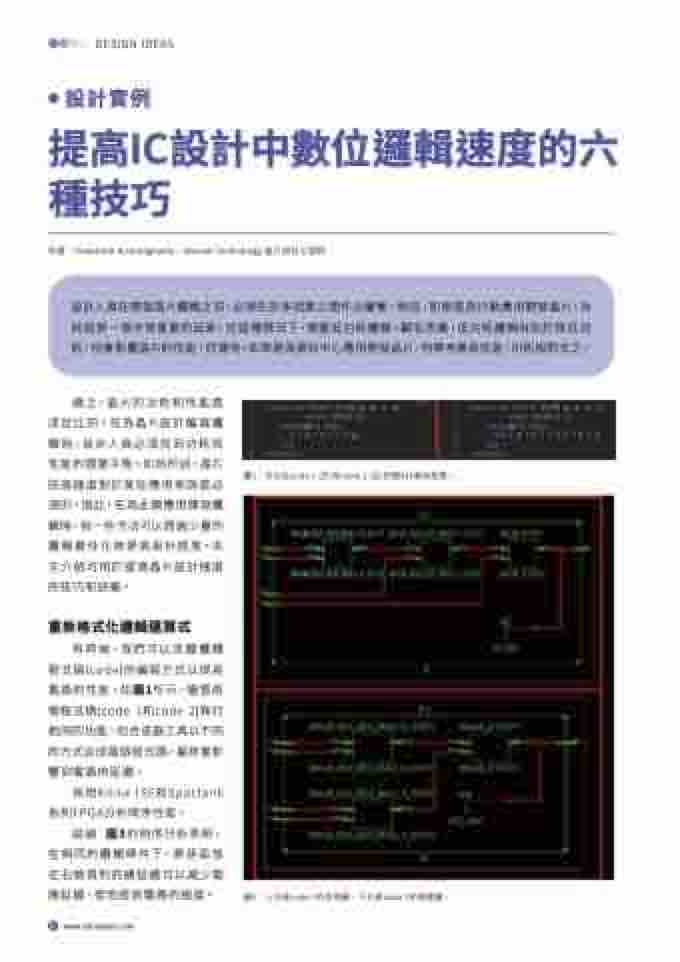

有時候,我們可以改變邏輯 程式碼(code)的編寫方式以提高 電路的性能。如圖1所示,儘管兩 個程式碼(code 1和code 2)執行 相同的功能,但合成器工具以不同 的方式合成兩個程式碼,最終會影 響到電路的延遲。

圖1:可以在code 1 (左)和code 2 (右)的第4行看到差異。

重新格式化邏輯運算式

採用Xilinx ISE和Spartan6 系列FPGA分析時序性能。

結論:圖3的時序分析表明, 在相同的邏輯條件下,將括弧放 在右側得到的總延遲可以減少電 路延遲,從而提高電路的速度。

圖2:上方是code 1的原理圖,下方是code 2的原理圖。

36 www.edntaiwan.com